linux vcs是编译型verilog仿真器,是一种用来进行仿真看波形的工具;其类似于windows下面的modelsim以及questasim等工具,以及quartus、vivado仿真的操作。

本教程操作环境:linux5.9.8系统、Dell G3电脑。

linux vcs是什么?

VCS工具的基本使用

VCS是在linux下面用来进行仿真看波形的工具,类似于windows下面的modelsim以及questasim等工具,以及quartus、vivado仿真的操作。

1.vcs的基本指令

vcs的常见指令后缀

| 指令 | 含义 |

|---|---|

-l readme.log | 用于将编译产生的信息放在log文件内 |

+v2k | 是使VCS兼容verilog 2001以前的标准 |

-debug_all | 用于产生debug所需的文件 |

-f verilog_file.f | 可将.f文件里的源码全部编译 |

-R | 编译后立即运行,即编译完成后立即执行 ./simv |

-Mupdate | 源文件有修改时,只重新编译有改动的**.v**文件,节约编译时间。 |

-sverilog | 打开对Systemverilog的支持,编译Systemverilog文件时使用。 |

-timescale=1ns/1ns | 设置仿真精度 |

-o simv_file | 编译默认产生的可执行文件为simv,可以使用 -o 更改可执行文件名。如果这里修改执行仿真时候就不是使用simv而是对应的o名字了。 |

simv的常见指令

| 指令 | 含义 |

|---|---|

./simv -l run.log | 执行的日志文件保存 |

./simv -gui | 以图形化界面打开 |

2.使用vcs的实例

采用的是全加器的官方教程,首先介绍不使用脚本的执行过程。

(1)先执行vcs加入对应的full_adder文件

vcs -sverilog -debug_all -timescale=1ns/1ps full_adder.v full_adder_tb.v -l com.log

这里先写full_adder.v 是因为tb文件需要调用它,所以把被调用的文件先写出来,这条语句会生成simv文件(如果使用了-o simv_file会生成对应的文件名字)。

(2)可以用./simv文件执行波形的界面,也可以采用下面指令以后台方式打开一个界面。

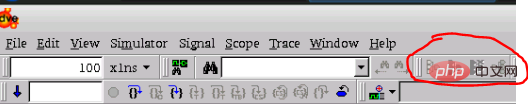

dve &或者 ./simv -l run.log -gui

(3)如果以./simv执行会直接看到波形文件,如果使用dve & 需要自行加入simv文件来查看波形,选中simulator->Setup,加入生成的simv文件。

在下方run all,如果没有给时间刻度这里会报错。没有报错,则说明我们的功能是完全正确无误的。右键加入波形文件,按f键显示波形。

(4)如下的四个按键作用

第一个: 追踪谁驱动该信号 ctrl+d

第二个: 追踪信号的值变换 ctrl+shift+d

第三个: 追踪未知态

第四个: 追踪用于驱动谁

3.makefile文件的写法

vcs的脚本写法可以帮助快递进行仿真得到波形文件。

其中.PHONY可以指定对应哪些关键词进行make操作。

.PHONY:vcs sim dve clean

OUTPUT = adder

VCS = vcs -sverilog +v2k -timescale=1ns/1ns \

-debug_all \

-o ${OUTPUT} \

-l compile.log \SIM = ./${OUTPUT} -l run.log

vcs: ${VCS} -f verilog_file.f

sim: ${SIM}dve:

dve -vpd vcdplus.vpd & clean: rm -rf *.log csrc simv* *.key *.vpd DVEfiles coverage *.vdb这样 make vcs执行vcs语句,make sim执行simv语句,make dve打开波形文件,make clean清除一些冗余文件。

其中,verilog_file.f是文件的列表,可以采用下面语句生成,这样将所有以v结尾的文件名写到目标文件中。

find -name ".*v" > file.list

以上就是linux vcs是什么的详细内容,更多请关注小君博客其它相关文章!

还没有评论,来说两句吧...